Rev B2, Page 1/27

# FEATURES

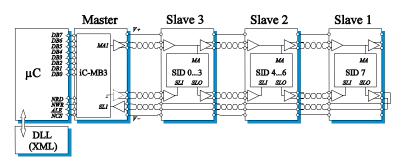

- Bidirectional *BiSS* sensor communication with up to 3 slaves

- Supports SSI protocol for unidirectional communication

- Synchronous sensor data acquisition with cyclic transfer at data rates of up to 10 Mbit/s

- Command and slave register operations during cyclic data transfers

- Data lengths of up to 64 bits for sensor data and multicycle data, independently scalable for each slave

- Automatic compensation of line delays, measurement and conversion times

- Data verification by CRC polynomials of up to 8 bits, adjustable per slave and data area

- Separate memory banks enable free controller access during BiSS sensor data transfers

- 32 bytes of intermediate memory to ease bidirectional slave register communications

- Parallel controller interface with an 8-bit data/address bus services Intel and Motorola devices

- ◆ Serial controller communication by SPI<sup>™</sup>-compatible mode

- Single 3 to 5V supply, industrial temperature range

Bidirectional device communi-

cation in multisensor systems

Position measurement with

linear or angular encoders

APPLICATIONS

٠

٠

Copyright © 2003, iC-Haus

Rev B2, Page 2/27

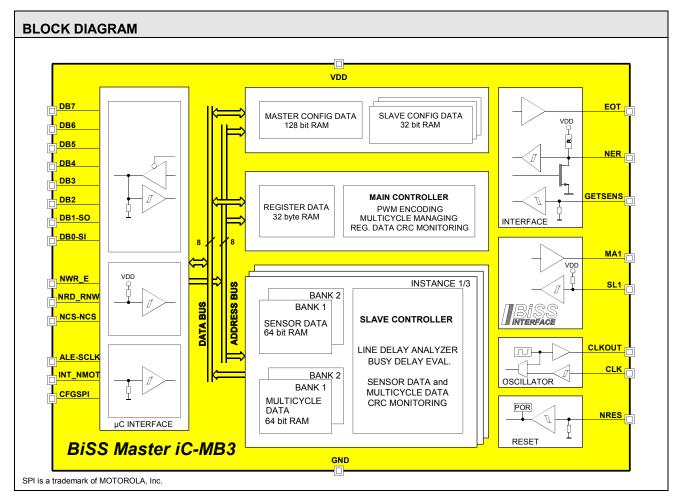

# DESCRIPTION

iC-MB3 is a single-chip *BiSS/SSI* interface controller featuring an 8-bit bus interface to industrial standard microcontrollers. An additional SPI interface mode also enables serial communication between iC-MB3 and the connected microcontroller.

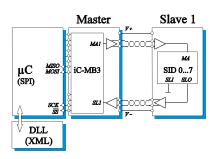

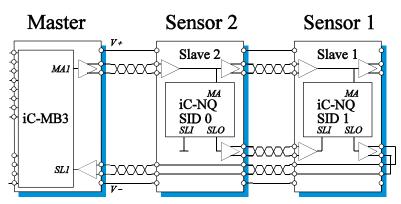

One to three *BiSS* devices can be attached to the sensor side of the device. These are connected up to clock line MA1 and data return line SL1 using RS422 transceivers (Figure 1). The *BiSS* devices can be connected directly in noise-free environments.

A maximum of three *BiSS* slaves is supported, each with their own independently scalable data sections encompassing:

- 1) Sensor data from 0 to 64 bits (for measurement data, alarms and warnings)

- 2) Multicycle data from 0 to 64 bits (for additional measurement data)

- Register data with 128 bytes per slave ID (e.g. for device parameters).

For both sensor and multicycle data iC-MB3 provides dual RAM memory banks for each slave, enabling flexible access to the microcontroller while new sensor data is being read in. A 32-byte intermediate memory supports register transfers.

Sensor data acquisition is started by a microcontroller command or via pin GETSENS. Alternatively, iC-MB3 can also read in new sensor data automatically; the cycle time in this instance can be set as required.

The end of sensor data acquisition and readin is signaled at pin EOT by a high; if faults occur during transmission pin NER signals a low. Errors in communication can be verified by the microcontroller via a status register; a system error message can also enter this register if bidirectional message pin NER is kept low by external intervention.

iC-MB3 generates a clock signal for sensor communication using an internal 20 MHz oscillator. The clock can also be supplied externally.

Figure 1: Point-to-point connection of iC-MB3 and one bus subscriber. This can use 1 to 8 slave IDs (SID).

Figure 2: Example network of iC-MB3 and three subscribers. All 8 possible slave IDs (SIDs) are used distributed.

# iC-MB3 *BiSS INTERFACE MASTER*, 1-Chan./3-Slaves

Rev B2, Page 3/27

**C**Haus

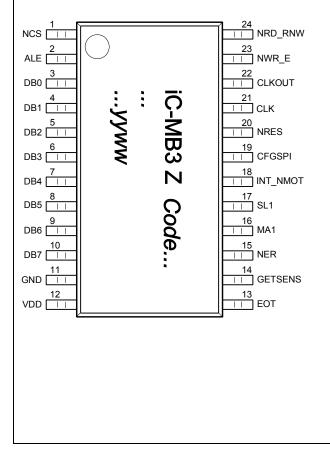

## PACKAGES TSSOP24 to JEDEC Standard

#### **PIN CONFIGURATION**

TSSOP24 4.4 mm, lead pitch 0.65 mm (top view)

#### **PIN FUNCTIONS** Function No. Name NCS Chip Select Input, low active 1 ALE-SCLK 2 Address Latch Enable Input 3 Data Bus DB0 4 DB1 Data Bus 5 DB2 Data Bus 6 DB3 Data Bus 7 DB4 Data Bus 8 DB5 Data Bus 9 DB6 Data Bus 10 Data Bus DB7 11 GND Ground +3.3 ... +5V Supply Voltage 12 VDD End-Of-Transmission Output 13 EOT GETSENS 14 Sensor Data Request Input NER Error Message Input/Output, low active 15 BiSS Clock/Data Line Output 16 MA1 17 SL1 **BiSS** Data Line Input 18 INT\_NMOT Mode Select (Intel = 1, Motorola = 0)\* 19 CFGSPI Serial/Parallel Mode Select Input (serial SPI = 1, parallel = 0) 20 NRES Reset Input, low active 21 CLK External Clock Input CLKOUT\*\* Clock Output 22 23 NWR\_E Write Input, low active (Intel) Enable Input, high active (Motorola) 24 NRD\_RNW Read Input, low active (Intel) Read/Not-Write Select Input (Motorola) Serial SPI Communication Mode (CFGSPI = 1): NCS Chip Select Input, low active 1 2 SCLK SPI Clock Input 3 SI SPI Serial Data Input SPI Serial Data Output 4 SO \* only when CLKENI = 1 else no signal

\*\* on SPI no effect

Rev B2, Page 4/27

# **ABSOLUTE MAXIMUM RATINGS**

| ltem | Symbol | Parameter                                     | Conditions                                                             | Fig. |      |      | Unit |

|------|--------|-----------------------------------------------|------------------------------------------------------------------------|------|------|------|------|

|      |        |                                               |                                                                        |      | Min. | Max. |      |

| G001 | VDD    | Supply Voltage VDD                            |                                                                        |      | -0.3 | 6    | V    |

| G002 | I(VDD) | Current in VDD                                |                                                                        |      | -20  | 30   | mA   |

| G003 | V()    | Voltage at all pins,<br>excluding VDD and GND | V()≤ VDD + 0.3 V                                                       |      | -0.3 | 6    | V    |

| G004 | I()    | Current in all pins<br>excluding VDD and GND  |                                                                        |      | -10  | 10   | mA   |

| E001 | Vesd() | ESD Susceptibility at all pins                | MIL-STD-883, Method 3015, HBM 100 pF discharged through 1.5 k $\Omega$ |      |      | 2    | kV   |

| TG1  | Tj     | Operating Junction Temperature                |                                                                        |      | -40  | 150  | °C   |

| TG2  | Ts     | Storage Temperature Range                     |                                                                        |      | -40  | 150  | °C   |

# THERMAL DATA

Operating Conditions: VDD = 3 ... 5 V

| ltem | Symbol | Parameter                                          | Conditions | Fig. |      |      |      | Unit |

|------|--------|----------------------------------------------------|------------|------|------|------|------|------|

|      |        |                                                    |            |      | Min. | Тур. | Max. |      |

| T1   | Та     | Operating Ambient Temperature<br>Range             |            |      | -25  |      | 85   | °C   |

|      |        | (extended range to -25 °C is available on request) |            |      |      |      |      |      |

Rev B2, Page 5/27

# **ELECTRICAL CHARACTERISTICS**

| ltem  | Symbol                                                    | Parameter                                                     | Conditions                                          | <b>⊺j</b><br>°C | Fig. | Min. | Тур. | Max. | Unit |

|-------|-----------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------|-----------------|------|------|------|------|------|

| Total | Device                                                    |                                                               |                                                     |                 |      |      |      |      |      |

| 001   | VDD                                                       | Permissible Supply Voltage                                    |                                                     |                 |      | 3    |      | 5.5  | V    |

| 002   | I(VDD)                                                    | Supply Current in VDD                                         | outputs not loaded,<br>f(CLK) = 20 MHz              |                 |      |      |      | 20   | mA   |

| 003   | Vc()hi                                                    | Clamp Voltage hi<br>at all pins excluding VDD, GND            | Vc()hi = V() - VDD, I() = 1 mA;<br>outputs tristate |                 |      | 0.3  |      | 1.6  | V    |

| 004   | Vc()lo Clamp Voltage lo<br>at all pins excluding VDD, GND |                                                               | I() = -1mA; outputs tristate                        |                 |      | -1.6 |      | -0.3 | V    |

| Cont  | rol Interface                                             | EOT, NER, GETSENS                                             | •                                                   |                 |      |      |      |      |      |

| 201   | Vs()hi                                                    | Saturation Voltage hi<br>at EOT                               | Vs()hi = VDD - V(); I() = -4 mA                     |                 |      |      |      | 400  | mV   |

| 202   | Vs()lo                                                    | Saturation Voltage lo<br>at EOT, NER                          | l() = 4 mA                                          |                 |      |      |      | 420  | mV   |

| 203   | Vt()hi                                                    | Threshold Voltage hi<br>at NER, GETSENS                       |                                                     |                 |      |      |      | 2    | V    |

| 204   | Vt()lo                                                    | Threshold Voltage lo<br>at NER, GETSENS                       |                                                     |                 |      | 0.8  |      |      | V    |

| 205   | Vt()hys                                                   | Threshold Voltage Hysteresis<br>at NER, GETSENS               |                                                     |                 |      | 300  | 500  |      | mV   |

| 206   | lpu()                                                     | Pull-Up Current at NER<br>vs. VDD                             | V() = 0 VDD - 1.5 V                                 |                 |      | -600 | -300 | -60  | μA   |

| 207   | lpd()                                                     | Pull-Down Current at GETSENS vs. GND                          | V() = 1.5 V VDD                                     |                 |      | 4    | 35   | 70   | μA   |

| BiSS  | Interface: N                                              | MA1, SL1                                                      |                                                     |                 |      |      |      |      |      |

| 301   | Vs(MA1)hi                                                 | Saturation Voltage hi                                         | Vs()hi = VDD - V(); I() = -4 mA                     |                 |      |      |      | 400  | mV   |

| 302   | Vs(MA1)lo                                                 | Saturation Voltage lo                                         | l() = 4 mA                                          |                 |      |      |      | 420  | mV   |

| 303   | Vt(SL1)hi                                                 | Threshold Voltage hi                                          |                                                     |                 |      |      |      | 2    | V    |

| 304   | Vt(SL1)lo                                                 | Threshold Voltage lo                                          |                                                     |                 |      | 0.8  |      |      | V    |

| 305   | Vt(SL1)hys                                                | Threshold Voltage Hysteresis                                  |                                                     |                 |      | 300  | 500  |      | mV   |

| 306   | Ipu(SL1)                                                  | Pull-Up Strom vs. VDD                                         | V() = 0 VDD - 1.5 V                                 |                 |      | -70  | -35  | -5   | μA   |

|       | iterface: bid<br>INT_NMOT,                                | lirectional data bus DB7 0, Inj<br>CFGSPI                     | outs NWR_E, NRD_RNW, NCS,                           |                 |      |      |      |      |      |

| 401   | Vs()hi                                                    | Saturation Voltage hi<br>at DB70                              | Vs()hi = VDD - V(); I() = -4 mA                     |                 |      |      |      | 400  | mV   |

| 402   | Vs()lo                                                    | Saturation Voltage lo<br>at DB70                              | l() = 4 mA                                          |                 |      |      |      | 420  | mV   |

| 403   | Vt()hi                                                    | Threshold Voltage hi                                          |                                                     |                 |      |      |      | 2    | V    |

| 404   | Vt()lo                                                    | Threshold Voltage lo                                          |                                                     |                 |      | 0.8  |      |      | V    |

| 405   | Vt()hys                                                   | Threshold Voltage Hysteresis                                  |                                                     |                 |      | 300  | 500  |      | mV   |

| 406   | lpd()                                                     | Pull-Down Current at DB70,<br>ALE, CFGSPI, INT_NMOT<br>to GND | V() = 1.5 V VDD                                     |                 |      | 4    | 35   | 70   | μA   |

| 407   | lpu()                                                     | Pull-Up Current at NRD_RNW,<br>NWR_E, NCS vs.VDD              | V() = 0 VDD-1.5 V                                   |                 |      | -70  | -35  | -4   | μA   |

Rev B2, Page 6/27

# **ELECTRICAL CHARACTERISTICS**

| Operating Conditions: VDD = 3 5.5 V, | Γj = -25 +125 °C, unless otherwise noted |

|--------------------------------------|------------------------------------------|

|--------------------------------------|------------------------------------------|

| ltem  | Symbol       | Parameter                                | Conditions                    | Tj | Fig. |      |      |      | Unit |

|-------|--------------|------------------------------------------|-------------------------------|----|------|------|------|------|------|

|       |              |                                          |                               | °C |      | Min. | Тур. | Max. |      |

| Oscil | llator: CLK, | CLKOUT                                   |                               |    |      |      |      |      |      |

| 501   | f(CLK)       | Permissible Clock Rate at CLK            |                               |    |      |      | 20   | 25   | MHz  |

| 502   | f(CLKOUT)    | Oscillator Clock Frequency               | VDD = 5 V, CLKENI = 1         |    |      |      | 20   |      | MHz  |

| 503   | Vt(CLK)hi    | Threshold Voltage hi                     |                               |    |      |      |      | 2    | V    |

| 504   | Vt(CLK)lo    | Threshold Voltage lo                     |                               |    |      | 0.8  |      |      | V    |

| 505   | Vt(CLK)hys   | Threshold Voltage Hysteresis             |                               |    |      | 300  | 500  |      | mV   |

| 506   | lpd()        | Pull-Down Current at CLK                 | V() = 1.5 V VDD               |    |      | 4    | 35   | 70   | μA   |

| 507   | Vs()hi       | Saturation Voltage hi at CLKOUT          | Vs()hi = VDD- V(); I()= -4 mA |    |      |      |      | 400  | mV   |

| 508   | Vs()lo       | Saturation Voltage lo at CLKOUT          | I()= 4 mA                     |    |      |      |      | 420  | mV   |

| 509   | lsc()hi      | Short-Circuit Current hi at<br>CLKOUT    | V() = 0                       |    |      | -30  | -12  | -4   | mA   |

| 510   | lsc()lo      | Short-Circuit Current lo at<br>CLKOUT    | V() = VDD                     |    |      | 5    | 23   | 50   | mA   |

| Rese  | t: NRES      |                                          |                               |    |      |      |      |      |      |

| 601   | VDDoff       | Undervoltage Reset                       | VDD decreasing                |    |      |      | 1.6  |      | V    |

| 602   | VDDon        | Undervoltage Release                     | VDD increasing                |    |      |      | 1.75 |      | V    |

| 603   | VDDhys       | Undervoltage Hysteresis                  | VDDhys = VDDon - VDDoff       |    |      |      | 100  |      | mV   |

| 604   | Vt()hi       | Threshold Voltage hi                     |                               |    |      |      |      | 2    | V    |

| 605   | Vt()lo       | Threshold Voltage lo                     |                               |    |      | 0.8  |      |      | V    |

| 606   | Vt()hys      | Threshold Voltage Hysteresis             |                               |    |      | 300  | 500  |      | mV   |

| 607   | lpd()        | Pull-Down Current                        | V() = 1.5 V VDD               |    |      | 4    | 35   | 70   | μA   |

| 608   | td()res      | Required Reset Pulse Duration<br>at NRES |                               |    |      | 250  |      |      | ns   |

Rev B2, Page 7/27

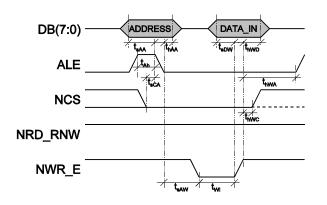

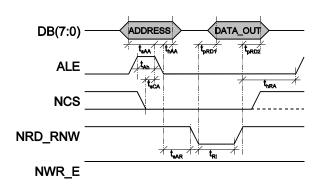

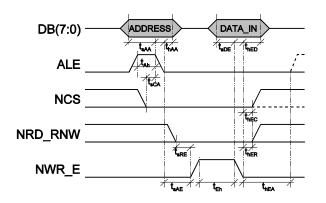

# OPERATING REQUIREMENTS: µC Interface, INTEL mode

Operating conditions: CFGSPI = 0, INT\_NMOT = 1 VDD = 3 ... 5.5V, Ta = -25 ... 85 °C; input levels lo = 0 ... 0.45 V, hi = 2.4 V ... VDD

| ltem | Symbol       | Parameter                                                            | Conditions | Fig. |      |      | Unit |

|------|--------------|----------------------------------------------------------------------|------------|------|------|------|------|

|      |              |                                                                      |            |      | Min. | Max. |      |

| 101  | tsAA         | Setup Time:<br>Address stable before ALE hi⊸lo                       |            | 3/4  | 15   |      | ns   |

| 102  | tAh          | Signal Duration:<br>ALE at high level                                |            | 3/4  | 10   |      | ns   |

| 103  | tsCA         | Setup Time:<br>NCS hi⊣lo until ALE hi⊣lo                             |            | 3/4  | 10   |      | ns   |

| 104  | thAA         | Hold Time:<br>Address stable after ALE hi⊸lo                         |            | 3/4  | 15   |      | ns   |

| 105  | tsAW         | Setup Time:<br>ALE hi→lo until NWR_E hi→lo                           |            | 3    | 0    |      | ns   |

| 106  | twi          | Signal Duration:<br>NWR_E at low level                               |            | 3    | 10   |      | ns   |

| 107  | tsDW         | Setup Time:<br>Data stable before NWR_E lo⊸hi                        |            | 3    | 15   |      | ns   |

| 108  | thWD         | Hold Time:<br>Data stable after NWR_E lo→hi                          |            | 3    | 0    |      | ns   |

| 109  | thWC         | Hold Time:<br>NCS lo after NWR_E lo∽hi                               |            | 3    | 0    |      | ns   |

| 110  | thWA<br>thRA | Hold Time:<br>ALE lo after NWR_E lo→hi                               | NCS = lo   | 3/4  | 15   |      | ns   |

| 111  | tsAR         | Setup Time:<br>ALE hi→lo until NRD_RNW hi→lo                         |            | 4    | 0    |      | ns   |

| 112  | trı          | Signal Duration:<br>NRD_RNW at low level                             |            | 4    | 70   |      | ns   |

| 113  | tpRD1        | Propagation Delay:<br>Data stable after NRD_RNW hi→lo                |            | 4    | 0    | 25   | ns   |

| 114  | tpRD2        | Propagation Delay:<br>Data Bus high impedance after<br>NRD_RNW lo⊸hi |            | 4    | 0    | 25   | ns   |

Figure 3: Write cycle (Intel Mode)

Rev B2, Page 8/27

## **OPERATING REQUIREMENTS: µC Interface, MOTOROLA mode**

Operating conditions: CFGSPI = 0, INT\_NMOT = 0

VDD = 3 ... 5.5V, Ta = -25 ... 85 °C; input levels lo = 0 ... 0.45 V, hi = 2.4 V ... VDD

| ltem | Symbol | Parameter                                                          | Conditions | Fig. |      |      | Unit |

|------|--------|--------------------------------------------------------------------|------------|------|------|------|------|

|      |        |                                                                    |            |      | Min. | Max. |      |

| 120  | tsAA   | Setup Time:<br>Address stable before ALE hi⊸lo                     |            | 5/6  | 15   |      | ns   |

| 121  | tAh    | Signal Duration:<br>ALE at high level                              |            | 5/6  | 10   |      | ns   |

| 122  | tsCA   | Setup Time:<br>NCS hi⊣lo until ALE hi⊣lo                           |            | 5/6  | 10   |      | ns   |

| 123  | thAA   | Hold Time:<br>Address stable after ALE hi⊣lo                       |            | 5/6  | 15   |      | ns   |

| 124  | tsAE   | Setup Time:<br>ALE hi⊸lo until NWR_E lo⊸hi                         |            | 5/6  | 0    |      | ns   |

| 125  | tsRE   | Setup Time:<br>NRD_RNW lo→hi until NWR_E lo→hi                     |            | 5/6  | 0    |      | ns   |

| 126  | tEh    | Signal Duration:<br>NWR_E at high level                            |            | 5/6  | 10   |      | ns   |

| 127  | tsDE   | Setup Time:<br>Data stable before NWR_E hi⊸lo                      |            | 5    | 15   |      | ns   |

| 128  | thED   | Hold Time:<br>Data stable before NWR_E hi⊸lo                       |            | 5    | 0    |      | ns   |

| 129  | thEC   | Hold Time:<br>NCS lo after NWR_E hi⊣lo                             |            | 5/6  | 0    |      | ns   |

| 130  | thER   | Hold Time:<br>NRD_RNW lo after NWR_E hi→lo                         |            | 5/6  | 0    |      | ns   |

| 131  | tpED1  | Propagation Delay:<br>Data stable after NWR_E lo→hi                |            | 6    | 0    | 25   | ns   |

| 132  | tpED2  | Propagation Delay:<br>Data bus high impedance after<br>NWR_E hi⊣lo |            | 6    | 0    | 25   | ns   |

| 133  | thEA   | Hold Time:<br>NWR_E hi⊸lo before ALE lo⊸hi                         | NCS = Io   | 5/6  | 0    |      | ns   |

Figure 5: Write cycle (Motorola Mode)

Figure 6: Read cycle (Motorola Mode)

Rev B2, Page 9/27

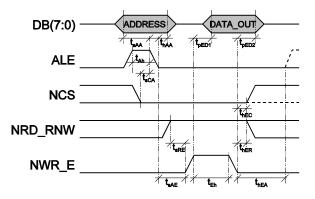

## OPERATING REQUIREMENTS: µC Interface, SPI mode

Operating conditions: CFGSPI = 1

VDD = 3 ... 5.5V, Ta = -25 ... 85 °C; input levels lo = 0 ... 0.45 V, hi = 2.4 V ... VDD

| ltem | Symbol | Parameter                                                   | Conditions | Fig. |      | _    | Unit |

|------|--------|-------------------------------------------------------------|------------|------|------|------|------|

|      |        |                                                             |            |      | Min. | Max. |      |

| 140  | tsCCL  | Setup Time:<br>NCS hi⊣lo until SCLK/ALE lo→hi               |            | 0.29 | 10   |      | ns   |

| 141  | tsDCL  | Setup Time:<br>SI/DB0 stable before SCLK/ALE lo-hi          |            | 0.29 | 15   |      | ns   |

| 142  | thDCL  | Hold Time:<br>SI/DB0 stable after SCLK/ALE lo⊸hi            |            | 0.29 | 0    |      | ns   |

| 143  | tCLh   | Signal Duration SCLK/ALE hi                                 |            | 7a/b | 10   |      | ns   |

| 144  | tc⊔    | Signal Duration SCLK/ALE lo                                 |            | 7a/b | 10   |      | ns   |

| 145  | thCLC  | Hold Time:<br>NCS lo after SCLK/ALE lo⊸hi                   |            | 7a/b | 0    |      | ns   |

| 146  | tCSh   | Signal Duration NCS hi                                      |            | 7a/b | 0    |      | ns   |

| 147  | tpCLD  | Propagation Delay:<br>SO/DB1 stable after SCLK/ALE hi⊸lo    |            | 7b   | 0    | 25   | ns   |

| 148  | tpCSD  | Propagation Delay: SO/DB1 high<br>impedance after NCS lo∽hi |            | 7b   | 0    | 25   | ns   |

Figure 7: µC interface in SPI mode with write cycle (top) and read cycles (bottom).

Rev B2, Page 10/27

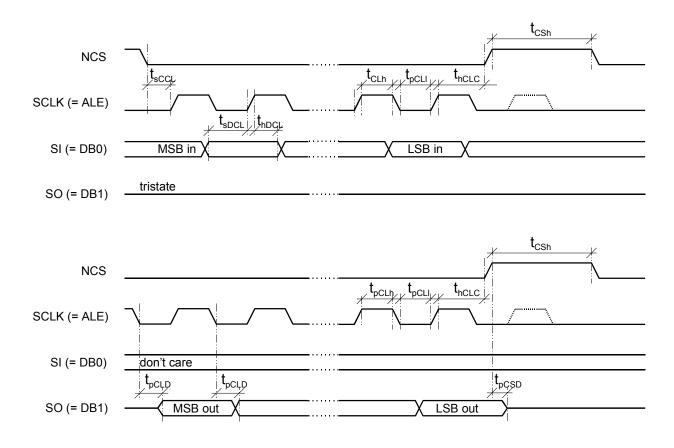

#### **OPERATING REQUIREMENTS:** BiSS Interface

Operating conditions: Register bit SELSSI = 0

VDD = 3 ... 5.5 V, Ta = -25 ... 85 °C; input levels lo = 0 ... 0.45 V, hi = 2.4 V ... VDD

| ltem  | Symbol        | Parameter                                                                                      | Conditions                                                          | Fig. |      |            | Unit     |

|-------|---------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|------|------------|----------|

|       |               |                                                                                                |                                                                     |      | Min. | Max.       |          |

| Sens  | or Mode       |                                                                                                |                                                                     |      |      |            |          |

| 160   | TMAS          | Clock Period                                                                                   | FreqSens via FREQ(4:0) selected in accordance with table on page 17 | 8    | 2    | 320        | 1/f(CLK) |

| 161   | tMASI         | Clock Signal Lo Level Duration                                                                 |                                                                     | 8    |      | 50         | % TMAS   |

| 162   | tMASh         | Clock Signal Hi Level Duration                                                                 |                                                                     | 8    |      | 50         | % Tmas   |

| 163   | tpLine        | Permissible Line Delay                                                                         |                                                                     | 8    | 0    | indefinite |          |

| 164   | ∆tpL          | Permissible Propagation Delay of<br>Subsequent Clock Cycles vs. 1 <sup>st</sup><br>Clock Cycle | ∆tpL = max( tpLine - tpLx ); x= 1 n                                 | 8    |      | 25         | % Tmas   |

| 165   | Ttos          | Permissible Timeout (Slave)                                                                    |                                                                     | 8    | 55   |            | % Tmas   |

| Regis | ster Mode'    | •                                                                                              |                                                                     |      |      |            |          |

| 165   | Tmar          | Clock Period                                                                                   | FreqReg via FREQ(7:5) selected in accordance with table on page 17  | 9    | 2    | 256        | TMAS     |

| 166   | <b>t</b> MA0h | "Logic 0" Hi Level Duration                                                                    |                                                                     | 9    |      | 25         | % Tmar   |

| 167   | tMA1h         | "Logic 1" Hi Level Duration                                                                    |                                                                     | 9    |      | 75         | % Tmar   |

| 168   | <b>t</b> MAth | Clock Signal Hi Level Duration                                                                 | register data readout                                               | 9    |      | 50         | % Tmar   |

| 169   | tsSL          | Setup Time:<br>SL1 stable before MA1 lo⊸hi                                                     |                                                                     | 9    | 30   |            | ns       |

| 170   | thSL          | Hold Time:<br>SL1 stable before MA1 lo⊸hi                                                      |                                                                     | 9    | 20   |            | ns       |

| 171   | Ttor          | Permissible Timeout (Slave)                                                                    |                                                                     | 9    | 80   |            | % Tmar   |

\*) For clocking to occur in register mode the slaves must have signaled that they are ready for register mode communication (see page 17).

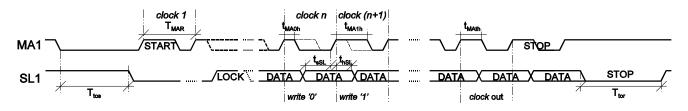

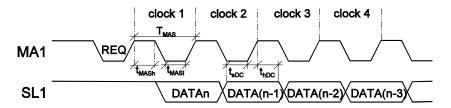

Figure 8: Timing diagram of sensor mode

Figure 9: Timing diagram of register mode

#### **Evaluating SL1 Signals**

In *BiSS* mode delay times of longer than one clock cycle are permissible, with the result that line delays during communication are negligible. Evaluation of the sensor response is delayed until the first falling edge at SL1 while at MA1 the clock signal continues to be output.

Within one MA1 clock cycle four equally distributed sampling instances are available. Following the falling edge at SL1, the slave's acknowledge signal, the SL1 level is evaluated two sampling instances on, close to the center of the transmitted bit.

Rev B2, Page 11/27

# OPERATING REQUIREMENTS: BiSS Interface (SSI mode)

Operating conditions: Register bit SELSSI = 1;

VDD = 3 ... 5.5 V, Ta = -25 ... 85 °C; input levels lo = 0 ... 0.45 V, hi = 2.4 V ... VDD

| Item | Symbol | Parameter                                  | Conditions                                                           | Fig. |       |      | Unit     |

|------|--------|--------------------------------------------|----------------------------------------------------------------------|------|-------|------|----------|

|      |        |                                            |                                                                      |      | Min.  | Max. |          |

| 180  | TMAS   | Clock Period                               | FreqSens über FREQ(4:0) selected in accordance with table on page 17 | 10   | 2 320 |      | 1/f(CLK) |

| 181  | tMASh  | Clock Signal Hi Level Duration             |                                                                      | 10   | 50    |      | %Tмаs    |

| 182  | tMASI  | Clock Signal Lo Level Duration             |                                                                      | 10   | 50    |      | %Tмаs    |

| 183  | tsDC   | Setup Time:<br>SL1 stable before MA1 lo⊸hi |                                                                      | 10   | 30    |      | ns       |

| 183  | thDC   | Hold Time:<br>SL1 stable before MA1 lo⊸hi  |                                                                      | 10   | 10    |      | ns       |

Figure 10: Timing diagram of SSI mode.

# **Evaluating SL1 Signals**

In *BiSS* interface SSI mode SL1 values are sampled with the rising edge at MA1. An overall delay of the sensor response to the clock at MA1, caused by process times in the sensor or transmission times, is permissible up to the length of one clock cycle.

Rev B2, Page 12/27

# **DESCRIPTION OF FUNCTIONS**

iC-MB3 must be configured in accordance with the sensors connected to it; to this end a special area of memory has been included in the device. The other memory banks are used for the interim storage of incoming slave data or of slave data yet to be transmitted.

iC-MB3's second main component is its logic blocks which enable communication with the controller and generate the *BiSS* interface protocol on the slave side of the chip.

#### **Microcontroller Interface**

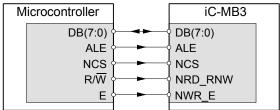

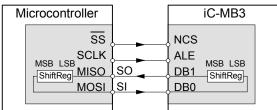

Via pins CFGSPI and INT\_NMOT iC-MB3 can be configured for operation with an SPI-competent microcontroller, an Intel 8051 controller or a 68HC11 Motorola controller.

Here, 8-bit multiplex mode is used, in which the bidirectional data bus alternately transmits addresses and data in blocks of 8 bits (see Figures 3 to 6).

| Communication Modes |          |                                |  |  |  |  |

|---------------------|----------|--------------------------------|--|--|--|--|

| CFGSPI              | INT_NMOT | Mode                           |  |  |  |  |

| 0                   | 0        | Motorola 68HC11                |  |  |  |  |

| 0                   | 1        | Intel 8051                     |  |  |  |  |

| 1                   | -        | SPI<br>(polarity= 0, phase= 0) |  |  |  |  |

Intel mode

| Microcontroller |     | iC-MB3  |

|-----------------|-----|---------|

| DB(7:0)         | →→  | DB(7:0) |

| ALE             |     | ALE     |

| NCS C           | →→→ | NCS     |

| NRD 🤇           |     | NRD_RNW |

| NWR             |     | NWR_E   |

SPI mode

Figure 11: Wiring diagram for the microcontroller and iC- MB3.

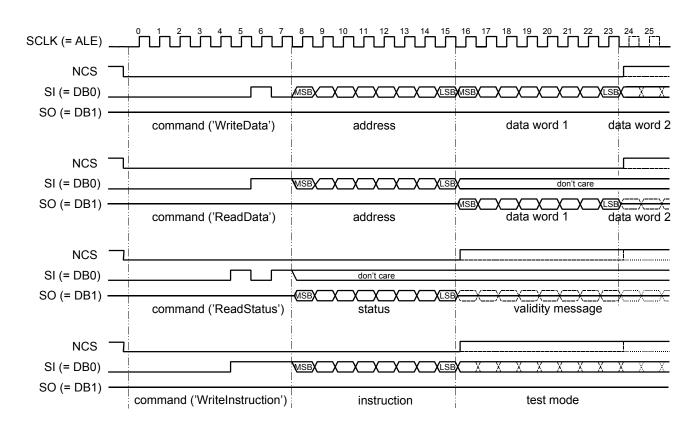

When operated in conjunction with an SPI controller pin ALE is used as a clock input (SCK) and pin NCS as an enable input (NCS), with DB0 as the data input (SI) and DB1 as the data output (SO). Data is transmitted serially in successive blocks of 8 bits (command, address and data).

Four commands are available. These are WriteData (0000 0010b), ReadData (0000 0011b), ReadStatus (0000 0101b) and WriteInstruction (0000 0111b). The first two commands can be used to write data to or read data from iC-MB3's registers. The latter two commands are truncated write and read commands where the start address is fixed (namely that of the command register to address 244 and that of the status register to address 240). This means that it is not necessary to give an address, with the data directly adhering to the command.

With all commands it is possible to transmit several bytes of data consecutively if the NCS signal is not reset and ALE/SCK continues to be clocked. The address transmitted (240 for ReadStatus and 244 for WriteInstruction) is then the start address which is internally increased by 1 following each transmitted byte.

Rev B2, Page 13/27

Figure 12: SPI transmission protocol (polarity 0, phase 0)

iC-MB3 target specification BiSS INTERFACE MASTER, 1-Chan./3-Slaves

Rev B2, Page 14/27

# **BiSS(SSI)** Interface Configurations

| Device Regi           | sters                                                |                                                                        |                                                             |                                          |                    |

|-----------------------|------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------|--------------------|

| Address <sup>1)</sup> | Description                                          |                                                                        |                                                             |                                          | Dir. <sup>2)</sup> |

| 00 63                 | Sensor Data - 64 bits per Slave                      |                                                                        |                                                             |                                          | in/out             |

|                       | Slave 1<br>Addresses 0700;<br>Iowest byte in Adr. 00 | <b>Slave 2</b><br>Addresses 1508;<br>lowest byte in Adr. 08            | <b>Slave 3</b><br>Addresses 2316;<br>lowest byte in Adr. 16 | Adr. 6324<br>reserved for<br>slaves 48   |                    |

| 64 127                | 64 127 Multicycle Data (MCD) - 64 bits per Slave     |                                                                        |                                                             |                                          | in/out             |

| 128 191               |                                                      | Slave 2<br>Addresses 7972;<br>lowest byte in Adr. 72<br>ata (32 bytes) | Slave 3<br>Addresses 8780;<br>Iowest byte in Adr. 80        | Adr. 12788<br>reserved for<br>slaves 48  | bidir              |

|                       |                                                      | or additional register dat                                             | a                                                           |                                          |                    |

| 192 223               | Slave Configuration Da                               | ata - 32 bits per Slave                                                |                                                             |                                          | in                 |

|                       | Slave 1<br>Addresses 195192                          | Slave 2<br>Addresses 199196                                            | Slave 3<br>Addresses 203200                                 | Adr. 223204<br>reserved for<br>slaves 48 |                    |

| 224 229               | Configuration of Register Communication              |                                                                        |                                                             |                                          |                    |

| 230 239               | Configuration of Master                              |                                                                        |                                                             |                                          |                    |

| 240 255               | Status information and                               | command register                                                       |                                                             |                                          | in/out             |

<sup>1)</sup> All addresses are decimals unless otherwise stated.

$^{2)}\,$  Direction  $\,$  in:  $\,$  Can only be written to by the  $\mu C$

out: Can be read out only by the  $\mu$ C

in/out: Sections can be written to by the  $\mu$ C in part and only be read out in part

bidir: Can be written to and read out by the  $\mu$ C

Reserved address range for other master devices.

Rev B2, Page 15/27

| Sens   | Sensor Data, Multicycle Data and Slave Configuration |        |                 |                                        |       |       |       |          |       |       |       |

|--------|------------------------------------------------------|--------|-----------------|----------------------------------------|-------|-------|-------|----------|-------|-------|-------|

| A      | Address                                              |        |                 |                                        |       |       |       |          |       |       |       |

| SL1    | SL2                                                  | SL3    | Description     |                                        |       |       |       |          |       |       |       |

| 07     | 15                                                   | 23     |                 |                                        |       |       |       |          |       |       |       |

| <br>00 | <br>08                                               | <br>16 | Sensor Data - S | ensor Data - SDATA(630)                |       |       |       |          |       |       |       |

| 71     | 79                                                   | 87     |                 |                                        |       |       |       |          |       |       |       |

|        |                                                      |        | Multicycle Data | - MCData(6                             | 30)   |       |       |          |       |       |       |

| 64     | 72                                                   | 80     |                 |                                        |       |       | 1     | 1        | [     |       |       |

|        |                                                      |        | Configuration   | Bit 7                                  | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

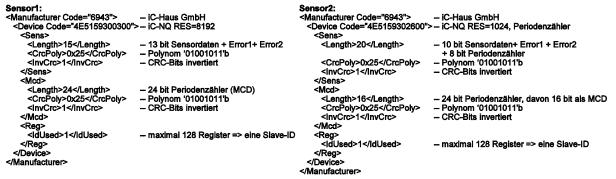

| 192    | 196                                                  | 200    | Sensor Data     | Sensor Data ACTnSENS ENSENS SDLEN(5:0) |       |       |       |          |       |       |       |

| 193    | 197                                                  | 201    | Sensor CRC      | Sensor CRC INVCRCS SENSCRCPOLY(7:1)    |       |       |       |          |       |       |       |

| 194    | 198                                                  | 202    | Multicycle Data | Multicycle Data GRAY ENMCD MCDLEN(5:0) |       |       |       |          |       |       |       |

| 195    | 199                                                  | 203    | MCD CRC         | INVCRCM                                |       |       | MCDCF | RCPOLY(7 | :1)   |       |       |

Key to the configuration bits:

| _ | ACTnSENS<br>ENSENS:<br>SDLEN:<br>INVCRCS:<br>SENSCRCPOLY: | Access to slave data: Read (0), Write (1)<br>Adaptation to slave sensor data: available (1), not available (0)<br>Bit length of sensor data <sup>1)</sup><br>Transmission of CRC bits for sensor data: inverted (1), not inverted (0)<br>CRC polynomial for verification of sensor data <sup>2)</sup> |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _ | GRAY                                                      | Gray/binary data conversion of sensor and multicycle data: active (1, required with SSI encoders), not active (0)                                                                                                                                                                                     |

|   | ENMCD:<br>MCDLEN:<br>INVCRCM:<br>MCDCRCPOLY:              | Adaptation to slave multicycle data: available (1), not available (0)<br>Bit length of multicycle data <sup>1)</sup><br>Transmission of CRC bits for multicycle data: inverted (1), not inverted (0)<br>CRC polynomial for verification of multicycle data <sup>2)</sup>                              |

- <sup>1)</sup> The length of the data should be given minus 1, i.e. for 64 data bits enter 63.

- <sup>2)</sup> If 0000 0000b is entered as the CRC polynomial, no cyclic redundancy check is carried out. As the last bit of a CRC polynomial is always 1 this is not entered in the polynomial register but added in the master. A CRC polynomial of up to 8 bits is thus possible. Should the full polynomial length not be required, the polynomial (minus its final 1) must be justified right and the spaces before it filled with zeros. For example, CRC polynomial 10 0011b is stored as 001 0001b.

Rev B2, Page 16/27

| Configur | ation Register Co | ommunic | ation      |           |             |            |            |       |       |

|----------|-------------------|---------|------------|-----------|-------------|------------|------------|-------|-------|

| Address  | Description       | Bit 7   | Bit 6      | Bit 5     | Bit 4       | Bit 3      | Bit 2      | Bit 1 | Bit 0 |

| 224      | Not used          | -       | -          | -         | -           | -          | -          | -     | -     |

| 225      | Not used          | -       | -          | -         | -           | -          | -          | -     | -     |

| 226      | Start Address     | WNR     |            |           | F           | REGADR(6:0 | )          |       |       |

| 227      | Count Of Bytes    | -       | -          | REGNUM(5) |             | F          | REGNUM(4:0 | )     |       |

| 228      | Channel Select    |         | CHSEL(8:1) |           |             |            |            |       |       |

| 229      | SlaveID           | -       | REGVERS    | S         | SLAVEID(2:0 | )          | -          | -     | -     |

| Configur  | ation Master                      |       |       |       |        |          |       |       |       |

|-----------|-----------------------------------|-------|-------|-------|--------|----------|-------|-------|-------|

| Address   | Description                       | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

| 230       | Frequency Division                |       |       |       | FRE    | Q(7:0)   |       |       |       |

| 231       | Not used                          | -     | -     | -     | -      | -        | -     | -     | -     |

| 232       | Frequency Division<br>AutoGetsens |       |       |       | FREQA  | GS(7:0)  |       |       |       |

| 233       | Not used                          | -     | -     | -     | -      | -        | -     | -     | -     |

| Device ID | )                                 |       |       |       |        |          |       |       |       |

| 234       | Revision                          | 0     | 0     | 0     | 0      | 0        | 0     | 0     | 1     |

| 235       | Туре                              |       |       |       | 1000   | 0011b    |       |       |       |

| Configur  | ation Channel                     |       |       |       |        |          |       |       |       |

| 236       | Slave Location                    |       |       |       | SLAVEL | _OC(8:1) |       |       |       |

|           |                                   |       |       |       |        |          |       |       |       |

| 236 | Slave Location    |         |          |         | SLAVEL   | .OC(8:1) |          |         |          |

|-----|-------------------|---------|----------|---------|----------|----------|----------|---------|----------|

| 237 | Mode of Operation | SELSSI4 | BiSSMOD4 | SELSSI3 | BiSSMOD3 | SELSSI2  | BiSSMOD2 | SELSSI1 | BiSSMOD1 |

| 238 | Mode of Operation | SELSSI8 | BiSSMOD8 | SELSSI7 | BiSSMOD7 | SELSSI6  | BiSSMOD6 | SELSSI5 | BiSSMOD5 |

| 239 | Not used          | -       | -        | -       | -        | -        | -        | -       | -        |

Key to the configuration bits: - SELSSI:

BISSMOD:

Type of protocol: *Bi*SS (0), SSI (1) *Bi*SS protocol model: BiSS model A or B (0), BiSS-A/S (1)

| Status Inf | Status Information and Command Register |                 |                      |                  |               |          |                    |                    |                    |

|------------|-----------------------------------------|-----------------|----------------------|------------------|---------------|----------|--------------------|--------------------|--------------------|

| Address    | Description                             | Bit 7           | Bit 6                | Bit 5            | Bit 4         | Bit 3    | Bit 2              | Bit 1              | Bit 0              |

| 240        | Status Information                      | nERR            | nWDERR               | nMCDERR          | nSENSERR      | nREGERR  | REGEND             | MCDEND             | EOT                |

| 241        | Validity Messages 1,2)                  | SVALID4         | MVALID4              | SVALID3          | MVALID3       | SVALID2  | MVALID2            | SVALID1            | MVALID1            |

| 242        | Validity Messages 1,2)                  | SVALID8         | MVALID8              | SVALID7          | MVALID7       | SVALID6  | MVALID6            | SVALID5            | MVALID5            |

| 243        | Register<br>Messages                    | MCD-<br>TIMEOUT | REG <sup>2, 4)</sup> | REG-<br>BYTES(5) | REGBYTES(4:0) |          |                    |                    |                    |

| 244        | Command<br>Register                     | BREAK           | UCREAD-<br>SENS      | SWRAM-<br>BANK   | INIT          | REGCMD   | GETSENS0           | GETSENS1           | AGS                |

| 245        | Control Flages                          | MAv0            | MAf0                 | MAvS             | MAfS          | reserved | IDDQ 3)            | IFTEST 3)          | CLKENI             |

| 246        | Not used                                | -               | -                    | -                | -             | -        | -                  | -                  | -                  |

| 247        | Not used                                | -               | -                    | -                | -             | -        | -                  | -                  | -                  |

| 248        | Channel Status                          | REG4            | SL4                  | REG3             | SL3           | REG2     | SL2                | REG1               | SL1                |

| 249        | Channel Status                          | REG8            | SL8                  | REG7             | SL7           | REG6     | SL6                | REG5               | SL5                |

| 250        | MCD bits 2)                             | MCD8            | MCD7                 | MCD6             | MCD5          | MCD4     | MCD3 <sup>2)</sup> | MCD2 <sup>2)</sup> | MCD1 <sup>2)</sup> |

| 251255     | Not used                                | -               | -                    | -                | -             | -        | -                  | -                  | -                  |

Reserved addresses for master devices featuring a higher slave or channel count, or more memory for register data. Any attempt to write to this register sets register values to 0. Two memory banks available. iC-Haus device test only, set to 0. For iC-MB3 the register bit REG is equal to REG1.

Rev B2, Page 17/27

# **Configuration - Master**

#### **Master Clock**

The master clock, either generated by the basic clock of the internal 20 MHz oscillator (CLKENI = 1) or by an external clock oscillator (CLKENI = 0) which supplies pin CLK, is set with the aid of the frequency division register (address 230).

The clock frequency for both *BiSS* sensor and SSI modes is set via FREQ(4:0) in accordance with the table on the top right. With an external clock pulse of  $f_{CLK}$  = 20 MHz clock frequencies ranging from 62.5 kHz to 10 MHz can thus be selected for sensor data transmission.

Both *BiSS* and SSI devices recognize an idle bus at the end of a transmission cycle via a monoflop timeout elapsing (timeoutSENS, see *BiSS* protocol). The choice of possible clock frequency is thus limited as the duration of both the high and low level may not exceed the shortest timeout of all of the connected subscribers (slaves).

*BiSS* devices switch to register mode on recognizing that the bus is idle after a high-low transition at the clock input and signal this state back to the master on the data line.

The clock frequency in *BiSS* register mode is set via FREQ(7:5) and can lie within a range of ca. 244 Hz to 5 MHz. Here selection is also limited as with the above; a different monoflop timeout now recognizes the idle bus at the end of the cycle (timeoutREG, see *BiSS* protocol).

Additionally, *BiSS* devices generally only permit a lower clock frequency (such as 250 kHz maximum, for example) because the clock form has to be evaluated as a PWM signal.

#### Automatic request for sensor data

The frequency with which new requests for sensor data are sent to the slaves is set using FREQAGS according to the table on the right. With an external clock of 20 MHz sensor data request cycles ranging from 1  $\mu$ s to 4 ms are possible.

FREQAGS must be set in such a way that the distance between two requests for data is greater than a complete cycle; this consists of the transmission of a request, an acknowledge signal (including any line delays), a start bit (including process times), a register bit (optional), the sensor, CRC and MCD bits of each slave and the longest sensor timeout of all the slaves.

| (FreqSens) |                       |                       |

|------------|-----------------------|-----------------------|

| FREQ(3:0)  | FREQ(4) = 0           | FREQ(4) = 1           |

| 0          | f <sub>clk</sub> /2   | not permitted         |

| 1          | f <sub>cLκ</sub> /4   | f <sub>ськ</sub> /40  |

| 2          | f <sub>ськ</sub> /6   | f <sub>ськ</sub> /60  |

| 3          | f <sub>cLK</sub> ∕8   | f <sub>CLK</sub> /80  |

| 4          | f <sub>ськ</sub> /10  | f <sub>CLK</sub> /100 |

| 5          | f <sub>ськ</sub> /12  | f <sub>CLK</sub> /120 |

| 6          | f <sub>CLK</sub> 14   | f <sub>ськ</sub> 140  |

| 7          | f <sub>ськ</sub> /16  | f <sub>CLK</sub> /160 |

| 8          | f <sub>CLK</sub> /18  | f <sub>CLK</sub> /180 |

| 9          | f <sub>ськ</sub> /20  | f <sub>стк</sub> /200 |

| 10         | f <sub>сі к</sub> /22 | f <sub>стк</sub> /220 |

| 11         | f <sub>CLK</sub> /24  | f <sub>CLK</sub> /240 |

| 12         | f <sub>ськ</sub> /26  | f <sub>CLK</sub> /260 |

| 13         | f <sub>ськ</sub> /28  | f <sub>cur</sub> /280 |

| 14         | f <sub>CLK</sub> /30  | f <sub>cur</sub> /300 |

| 15         | f <sub>ськ</sub> /32  | f <sub>с∟к</sub> /320 |

Master Clock for BiSS Sensor Mode and SSI

A combination of FREQ(4) = 1 and FREQ(3:0) = 0 is not permitted; for a clock frequency of  $f_{CLK}/20$  FREQ(4) = 0 and FREQ(3:0) = 9 must be set.

| Master Clock for <i>Bi</i> SS Register Mode<br>(FreqReg) |                          |  |  |

|----------------------------------------------------------|--------------------------|--|--|

| FREQ(7:5)                                                | FreqReg                  |  |  |

| 0<br>1                                                   | FreqSens/2<br>FreqSens/4 |  |  |

| 2                                                        | FreqSens/8               |  |  |

| 3                                                        | FreqSens/16              |  |  |

| 4                                                        | FreqSens/32              |  |  |

| 5                                                        | FreqSens/64              |  |  |

| 6                                                        | FreqSens/128             |  |  |

| 7                                                        | FreqSens/256             |  |  |

| Automatic Sensor Data Request<br>(FreqAGS) |                        |                         |  |  |  |

|--------------------------------------------|------------------------|-------------------------|--|--|--|

| FREQAGS(6:0)                               | FREQAGS(7)= 0          | FREQAGS(7)= 1           |  |  |  |

| 0                                          | f <sub>сLK</sub> /20   | f <sub>ськ</sub> /625   |  |  |  |

| 1                                          | f <sub>сLK</sub> /40   | f <sub>ськ</sub> /1250  |  |  |  |

| 2                                          | f <sub>сLK</sub> /60   | f <sub>ськ</sub> /1875  |  |  |  |

|                                            |                        |                         |  |  |  |

| 125                                        | f <sub>cLK</sub> /2520 | f <sub>cLk</sub> /78750 |  |  |  |

| 126                                        | f <sub>CLK</sub> /2540 | f <sub>cLk</sub> /79375 |  |  |  |

| 127                                        | f <sub>CLK</sub> /2560 | f <sub>cLk</sub> /80000 |  |  |  |

iC-MB3 BiSS INTERFACE MASTER, 1-Chan./3-Slaves

Rev B2, Page 18/27

# **DATA STORAGE - Sensor and Multicycle Data**

So that new sensor data can be read in during controller accesses iC-MB3 has dual memory banks for sensor and multicycle data. While sensor data is being read into the first RAM, from the second RAM section the controller can read out the sensor data last read in. The relevant sensor data memory banks are swapped over at the end of the readin procedure; this can be prevented by the controller entering the command register bit UCREADSENS. The MCD memory banks are swapped once a complete MCD cycle has been transmitted if at the same time bit MCDEND changes to a 1 in the status register. In parallel with this the validity message register (address 241) and the bits REG and MCD (addresses 248 to 250) are also swapped.

#### Arrangement of sensor and multicycle data in the RAM

The sensor or multicycle data memory bank for each slave has 8 bytes of memory which can be interpreted as 64 bits of memory in the array xxxx111b to xxxxx000b. The sensor or multicycle data is written to memory area [SDLEN - 1:0] or [MCDLEN - 1:0], with SDLEN and MCDLEN marking the length of the relevant data. Should there be room in the available memory for the CRC bits, these are then also stored with the above data at positions [63:63 - (CRCLEN-1)].

| Example Slave 2: 20 bits of sensor data, 6 bits of CRC<br>13 bit of multicycle data, 5 bits of CRC=> total length of 26 bits<br>=> total length of 18 bits |                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Adr. 07 00:<br>Adr. 15 08:                                                                                                                                 | Sensor data Slave 1<br>Sensor data Slave 2 -<br>Adr. 15: SensCRC(5:0), not defined, not defined<br>Adr. 14: - not defined -<br>Adr. 13: - not defined -<br>Adr. 12: - not defined -<br>Adr. 11: - not defined -<br>Adr. 10: not defined, not defined, not defined, SensData(19:16)                                                   |  |  |  |  |  |

| Adr. 23 16:                                                                                                                                                | Adr. 9: SensData(15:8)<br>Adr. 8: SensData(7:0)<br>Sensor data Slave 3                                                                                                                                                                                                                                                               |  |  |  |  |  |

| <br>Adr. 71 64:<br>Adr. 79 72:                                                                                                                             | Multicycle data Slave 1<br>Multicycle data Slave 2 -<br>Adr. 79: MCDCRC(4:0), not defined, not defined, not defined<br>Adr. 78: - not defined -<br>Adr. 77: - not defined -<br>Adr. 76: - not defined -<br>Adr. 75: - not defined -<br>Adr. 74: - not defined -<br>Adr. 73: not defined, not defined, MCD(12:8)<br>Adr. 72: MCD(7:0) |  |  |  |  |  |

| Adr. 87 80:                                                                                                                                                | Multicycle data Slave 3                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

#### DATA STORAGE - register data

For the interim storage of register information read out from or to be written to the slaves iC-MB3 has an individual storage area (addresses 128 to 159) which can temporarily store up to 32 bytes of data. With just one single command this is then transmitted to a slave selected using SLAVEID(2:0) or requested from it as register data. The transmission of register data takes longer than that of sensor data so that the content of the sensor data and MCD RAM is then often obsolete.

Rev B2, Page 19/27

# STATUS INFORMATION and COMMAND REGISTER

| Addres | Address 240: Status Messages |                                                                                                                                     |         |  |  |  |  |  |

|--------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| Bit    | Designation                  | Function                                                                                                                            | Remarks |  |  |  |  |  |

| 7      | nERR                         | An error has occurred (low active), equivalent to the pin level at NER (see "Error messaging" on page 22)                           |         |  |  |  |  |  |

| 6      | nWDERR                       | Watchdog error (low active) on<br>- transmissions triggered by an automatic sensor data request<br>- transmissions of register data | 1       |  |  |  |  |  |

| 5      | nMCDERR                      | CRC error in the multicycle data (low active)                                                                                       | 2       |  |  |  |  |  |

| 4      | nSENSERR                     | CRC error in the sensor data (low active)                                                                                           | 2       |  |  |  |  |  |

| 3      | nREGERR                      | CRC error during the transmission of register data (low active)                                                                     | 3       |  |  |  |  |  |

| 2      | REGEND                       | End of register data transmission                                                                                                   |         |  |  |  |  |  |

| 1      | MCDEND                       | End of multicycle data transmission (cycle completed)                                                                               |         |  |  |  |  |  |

| 0      | EOT                          | End of transmission:<br>signals the end of sensor or register data transmission before<br>timed out                                 |         |  |  |  |  |  |

- 1. A watchdog error is triggered during the automatic transmission of sensor data if no new cycle could be initiated; bit AGS in the command register is reset and the automatic request for sensor data aborted. During the transmission of register data a watchdog error is triggered if the slave shows no response, i.e. if it does not answer the first falling master edge with a low or fails to generate a start bit.

- 2. If a sensor data or MCD error is signaled the faulty sensor can be verified by reading out address 241 (validity message).

- 3. If a register data error is generated the number of bytes transmitted correctly before the error occurred can be determined by reading out the register message REGBYTES (address 243, bits 5...0). In the event of error the transmission of data is terminated.

| Address 241: Validity Messages |             |                                            |         |  |  |  |  |

|--------------------------------|-------------|--------------------------------------------|---------|--|--|--|--|

| Bit                            | Designation | Function                                   | Remarks |  |  |  |  |

| 7                              | MVALID4     | Not used                                   | 1       |  |  |  |  |

| 6                              | SVALID4     | Not used                                   | 1       |  |  |  |  |

| 5                              | MVALID3     | Readout multicycle data from slave 3 valid | 1       |  |  |  |  |

| 4                              | SVALID3     | Readout sensor data from slave 3 valid     | 1       |  |  |  |  |

| 3                              | MVALID2     | Readout multicycle data from slave 2 valid | 1       |  |  |  |  |

| 2                              | SVALID2     | Readout sensor data from slave 2 valid     | 1       |  |  |  |  |

| 1                              | MVALID1     | Readout multicycle data from slave 1 valid | 1       |  |  |  |  |

| 0                              | SVALID1     | Readout sensor data from slave 1 valid     | 1       |  |  |  |  |

1. Any attempt to write to this register resets the validity messages.

Rev B2, Page 20/27

| Address 243: Register Messages |               |                                                                         |         |  |  |  |  |

|--------------------------------|---------------|-------------------------------------------------------------------------|---------|--|--|--|--|

| Bit                            | Designation   | Function                                                                | Remarks |  |  |  |  |

| 7                              | MCDTIMEOUT    | MCD timeout elapsed (1), not elapsed (0)                                | 1       |  |  |  |  |

| 6                              | REG           | Current register data bit at the slave operating on <i>BiSS</i> model C | 2       |  |  |  |  |

| 5                              | REGBYTES(5)   | Not used                                                                |         |  |  |  |  |

| 40                             | REGBYTES(4:0) | Number of register bytes transmitted correctly if an error occurs       | 3       |  |  |  |  |

- 1. A new request for multicycle data can only be made once the MCD timeout has elapsed; if a new MCD request is issued before this time the slaves operating on *BiSS* protocol model C will treat this as a register data transmission (see "Register communication in sensor mode").

- 2. During the data transmission in *BiSS* protocol model C format, where register data is transmitted together with sensor and multicycle data, the current register data bit in bit REG can be read out. Similar to the sensor data this bit also has a second storage section which allows the readout of bits transmitted during the last cycle while a new cycle is running. A swap occurs in parallel with that of the sensor data banks.

- 3. If no errors occur during transmission these bits are set to 0. Otherwise the number of register bytes successfully transmitted without error is displayed.

| Address 244: Command Register |             |                                                                                                 |         |  |  |  |  |

|-------------------------------|-------------|-------------------------------------------------------------------------------------------------|---------|--|--|--|--|

| Bit                           | Designation | Function                                                                                        | Remarks |  |  |  |  |

| 7                             | BREAK       | The current action is aborted (e.g. the clock at MA1 is stopped)                                |         |  |  |  |  |

| 6                             | UCREADSENS  | RAM bank swapping is blocked                                                                    |         |  |  |  |  |

| 5                             | SWRAMBANK   | All RAM banks and the validity message register are forcibly swapped                            |         |  |  |  |  |

| 4                             | INIT        | The sensor is initialized                                                                       |         |  |  |  |  |

| 3                             | REGCMD      | Executes transmissions of register data                                                         |         |  |  |  |  |

| 2                             | GETSENS0    | Single request for sensor data with a high cycle termination (no refreshing of multicycle data) |         |  |  |  |  |

| 1                             | GETSENS1    | Single request for sensor data with a low cycle termination (request to update multicycle data) |         |  |  |  |  |

| 0                             | AGS         | Start of automatic sensor data requests (AutoGetSens)                                           |         |  |  |  |  |

All bits with the exception of AGS, UCREADSENS and SWRAMBANK are independently deleted by the master once the command has been carried out.

All current actions can be aborted using the BREAK command so that a defined state can be resumed if one of the sensors proves faulty, for example.

During the readout of more than one sensor data register by the controller it is possible that the RAM banks in the master could be swapped over once a sensor data transmission is complete. So that the controller only reads related values bit UCREADSENS should be set at the start of the readout and returned at the end; this suppresses the RAM swap. With the start of a new sensor data cycle previous values are then overwritten by the new sensor data.

Each setting or deletion of bit SWRAMBANK forces the sensor data and MCD RAM banks to be swapped over. Data just input, for example, can then be read out if a cycle has ended during UCREADSENS = 1 (this is indicated by EOT in the status register switching to 1 during the suppression of the RAM swap).

Rev B2, Page 21/27

The sensor chain can be initiated using the command INIT. A set REG bit starts the transmission of register data between iC-MB3 and a sensor.

The transmission of sensor data can be triggered via bits GETSENS0 and GETSENS1. In both instances a new transmission process is initiated; the difference between the two commands lies in how the transmission cycle is ended. With GETSENS0 the cycle finishes with a high; GETSENS1 ends on a low which also files a request for multicycle data. In this case the previous MCD cycle must have ended (MCDEND = 1) and the multicycle data timeout must have elapsed (MCDTIMEOUT = 1).

When initializing the sensor data transmission via GETSENS0 = 1 and GETSENS1 = 1, the cycle finishes with a level determined by the REG bit entered (Address 243, bit 6), i.e. for REG = 0 with a high or for REG = 1 with a low. By this function register data can be transmitted to slaves operating on the *BiSS* protocol model C principle in parallel to the transmission of sensor data (see "Transmission of register data in sensor mode").

To enable the synchronized data conversion of several slaves at once, all of which have differing wake-up times (power save mode), a sensor data cycle which initially wakes all of the slaves can be started by explicitly setting the GETSENS1 bit. Once the slaves have confirmed their state of readiness by sending an MCD start bit, setting GETSENS1 a second time (following the end of the MCD timeout) forces the synchronous storage of multicycle data in all slaves (see general notes on the *BiSS* protocol).

If an AGS bit has been set sensor data is read in cyclically according to the cycle frequency set in register 232 (FREQAGS) without any further commands being issued by the controller. As soon as all of the slaves connected have finished transmitting multicycle data (MCDEND = 1, MCDTIMEOUT = 1) a new request for multicycle data is started automatically.

Registers start address (REGADR, address 226), number of bytes (REGNUM, address 227) and slave ID (SLAVEID, address 229) stipulate from which slave register address onwards how many bytes are to be written to or read out from which specific slave. A byte count of 0 entered for REGNUM signals the transmission of a single register value; a 31 indicates the transmission of 32 register values. In the register REGBYTES (address 243) a 0 is entered if communication has proved error free. In the event of error the number of registers correctly read or written is displayed.

iC-MB3 does not support autonomous register communication as with *BiSS* model C, thus it is imperative that address 229's bit REGVERS remain set to 0.

Rev B2, Page 22/27

#### Initialization

To initialize the bus subscribers and to allow them to find their position in the queue (and particularly so that the first slave recognizes its position as such) the master line must be set to 0 after a 1 period (longer than the longest sensor timeout). The slaves themselves signal that initialization has been successful with a 0 on line SL1.

During initialization internal counters and error flags in the master are deleted or set as appropriate. Should a slave prove faulty and not switch to 0 initialization must be aborted by a BREAK command.

Initialization ends when the MCD timeout flag is set (address 243); a request for multicycle data can thus be made in the next sensor data cycle.

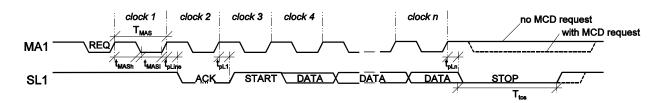

#### Communication in sensor mode

The transmission of sensor data begins when at pin MA1 the master outputs the clock signal with the clock frequency selected by FREQ. The line delay, i.e. the transmission propagation until an acknowledgement is generated at SL1, is determined from the second falling edge onwards.

While the clock continues to be output at MA1 the master waits for the slaves' start bit (1) signaling the start of data transmission. Following this the actual clocking out of sensor data begins, i.e. the sensors place a new bit on the SL1 line with each rising edge on the MA1 line.

The sensor data being input into the master and the ensuing sets of CRC data are written to the appropriate sensor data RAM. At the same time the new CRC value is calculated in accordance with InvSensCRC and using the CRC polynomial stored in the configuration RAM. Should, after entry of the last CRC bit, the system ascertain that transmission was faulty the relevant validity message in address 241 is deleted and error message nSENSERR set in the status register at address 240. At the same time the sensor data RAM banks are swapped.

If the sensor is MCD competent the MCD bit following the sensor data CRC is stored in the appropriate position in the relevant RAM bank. If a CRC code is to be calculated this is done simultaneously – in accordance with InvMCDCRC and using the CRC polynomial stored in the configuration RAM – and also saved to the RAM. With the last multicycle data CRC bit read in the transmission is checked for errors; if any are determined the relevant validity message bit is deleted.

At the end of the sensor data cycle, when the last bit of the longest multicycle data from all the connected sensors has been read in, the terminated MCD transmission is signaled by flag MCDEND and the MCD RAM banks are swapped over. The controller can now read out the current MCD values.

Each sensor data cycle ending with a request for multicycle data resets the MCD timeout counter. Each cycle without an MCD request raises the counter by 1 until after 14 consecutive cycles the MCDTIMEOUT bit is set. This makes it possible to differentiate between an MCD request and a register bit sent by a slave operating on *BiSS* protocol model C (see "Register communication in sensor mode").

#### Communication in register mode

Once the slaves have signaled their readiness for register communication (SL1 = 0) the addressing sequence is compiled, consisting of a start bit (1), the slave ID, the register address, the write/read flag, the inverted CRC calculated from this and a stop bit (0). This sequence is then transmitted bit by bit.

At the same time the ID distribution among the slaves is checked; should none of the slaves react (should SL1 not signal a 1 after 9 clock pulses) communication is aborted and a register error message generated (nREGERR = 0). The same happens if the slave response is not 0 after the 17<sup>th</sup> rising edge at MA1.

If a register value is to be transmitted to a slave transmission of the new register value begins after 17 clock pulses (i.e. following the transmission of the start bit, slave ID, register address, WNR, CRC and stop bit). This new register value consists of a start bit (1), the new contents of the register, the inverted CRC code and a stop

iC-MB3 BiSS INTERFACE MASTER, 1-Chan./3-Slaves

Rev B2, Page 23/27